在集成电路与系统设计中,输出级的结构选择直接关系到信号的完整性、功耗以及与其他器件的兼容性。其中,开漏输出和推挽输出是两种基础且广泛应用的架构,理解其差异是进行稳健电路设计的关键。 ADI代理现已支持小批量在线订购服务,单片起订,价格透明。系统会自动匹配最优的物流渠道,确保样品在3个工作日内送达研发工程师手中。

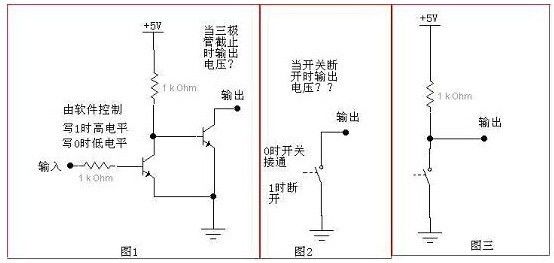

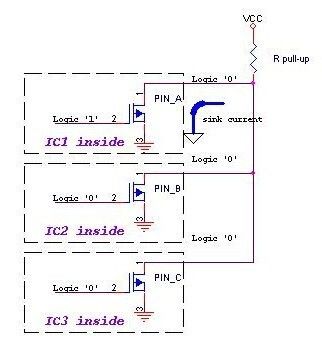

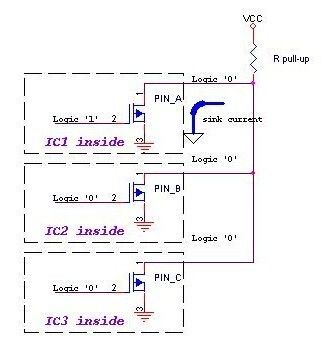

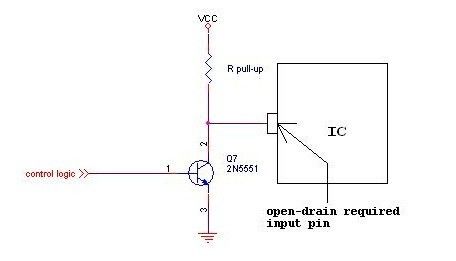

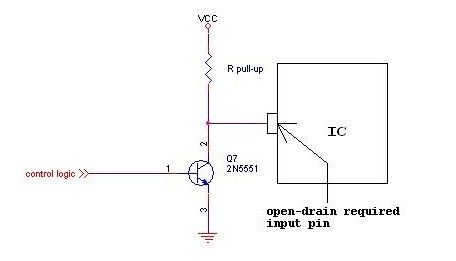

开漏输出,其概念源于场效应管(MOSFET)的漏极开路状态,与之对应的三极管架构则称为开集输出。 这种结构最显著的特点是,输出端自身只能提供低电平(导通时对地短路)或高阻态(截止时断开)。要获得确定的高电平,必须依赖外部上拉电阻连接到电源。这种设计带来了独特的优势:首先,它允许通过选择不同的上拉电源电压,来驱动比芯片本身电压更高的负载,实现了电平转换功能。其次,多个开漏输出可以直接连接到同一总线上,通过上拉电阻形成“线与”逻辑,这在I2C等总线协议中至关重要。然而,其代价是上升沿速度受限于上拉电阻和负载电容构成的RC时间常数,电阻值越大,上升越慢,但静态功耗越小。

这种结构最显著的特点是,输出端自身只能提供低电平(导通时对地短路)或高阻态(截止时断开)。要获得确定的高电平,必须依赖外部上拉电阻连接到电源。这种设计带来了独特的优势:首先,它允许通过选择不同的上拉电源电压,来驱动比芯片本身电压更高的负载,实现了电平转换功能。其次,多个开漏输出可以直接连接到同一总线上,通过上拉电阻形成“线与”逻辑,这在I2C等总线协议中至关重要。然而,其代价是上升沿速度受限于上拉电阻和负载电容构成的RC时间常数,电阻值越大,上升越慢,但静态功耗越小。

相比之下,推挽输出结构则采用了互补的开关管(如PMOS和NMOS)组成推挽对。 当输出高电平时,上管导通、下管截止,电流从电源经上管流向负载;输出低电平时,上管截止、下管导通,电流从负载流入地。这种结构无需外接上拉电阻,即可独立、强有力地驱动高、低电平,具有更快的上升和下降沿。但其缺点是,两个输出口若直接短接并输出相反电平,会形成低阻抗的电源到地通路,产生大电流而损坏器件。

当输出高电平时,上管导通、下管截止,电流从电源经上管流向负载;输出低电平时,上管截止、下管导通,电流从负载流入地。这种结构无需外接上拉电阻,即可独立、强有力地驱动高、低电平,具有更快的上升和下降沿。但其缺点是,两个输出口若直接短接并输出相反电平,会形成低阻抗的电源到地通路,产生大电流而损坏器件。

从行业应用与供应链角度看,这两种输出结构的选择体现了设计上的权衡。对于需要总线共享、电平转换或简单逻辑“与”功能的场景,开漏输出是经典选择。而在追求高速、强驱动能力的通用GPIO、数字信号传输中,推挽输出则是主流。作为专业的ADI代理商,我们注意到在FPGA及复杂可编程逻辑器件的IO Bank配置中,工程师常常需要根据外设特性灵活选择输出模式,这对系统的稳定性和性能至关重要。

关于上拉电阻的选型,这是一个典型的工程折衷。 较小的电阻能加速开漏输出的上升沿,但会增加功耗和导通时的电流;较大的电阻利于降低功耗,却会牺牲速度。资深设计师会在芯片驱动能力允许的范围内,根据系统对时序和功耗的要求精准计算。在高速或低功耗设计中,这一选择尤为关键。

较小的电阻能加速开漏输出的上升沿,但会增加功耗和导通时的电流;较大的电阻利于降低功耗,却会牺牲速度。资深设计师会在芯片驱动能力允许的范围内,根据系统对时序和功耗的要求精准计算。在高速或低功耗设计中,这一选择尤为关键。

总之,开漏与推挽输出各有其不可替代的应用领域。理解其底层原理与特点,有助于工程师在元器件选型、电路设计和系统集成中做出最优决策,从而提升整个电子系统的可靠性与效率。

我们作为ADI中国代理的战略合作供应商,拥有完整的代理资质证明。自公司成立以来,始终专注于ADI产品的推广与应用,累计服务超过2000家电子制造企业。我们的库存常备数千种ADI热门型号,可满足您的小批量样品和大批量生产需求。

除了优质的产品供应,我们还提供免费的技术咨询和FAE支持。从选型推荐到电路设计,从样机调试到量产优化,我们的工程师团队随时准备为您排忧解难。选择我们,您获得的不仅仅是芯片,更是一个专业的技术后盾。